# **Experience in the Design, Implementation and Use of a Retargetable Static Binary Translation Framework**

Cristina Cifuentes, Mike Van Emmerik, Norman Ramsey, and Brian Lewis

# **Experience in the Design, Implementation and Use of a Retargetable Static Binary Translation Framework**

Cristina Cifuentes, Mike Van Emmerik, Norman Ramsey, and Brian Lewis

SMLI TR-2002-105 January 2002

#### Abstract:

Binary translation, the process of translating binary executables, makes it possible to run code compiled for source (input) machine  $M_{\rm s}$  on target (output) machine  $M_{\rm t}$ . Unlike an interpreter or emulator, a binary translator makes it possible to approach the speed of native code on machine  $M_{\rm t}$ . Translated code may still run slower than native code because low-level properties of machine  $M_{\rm s}$  must often be modeled on machine  $M_{\rm t}$ .

The University of Queensland Binary Translation (UQBT) framework is a retargetable framework for experimenting with static binary translation on CISC and RISC machines. The system was built jointly by The University of Queensland and Sun Microsystems Laboratories in order to experiment with translations to and from different machines, to understand how to migrate applications from other UNIX®-based platforms to a (SPARC®, Solaris™) platform, and to experiment with translations from the current SPARC architecture to a future, not yet existing, version of the SPARC architecture.

This paper describes the overall design and architecture of the UQBT framework, the goals for the project, the resulting framework, experiences with translations across different machines, and lessons learned.

| © 2002 Sun Microsystems, Inc., Harvard University, and The University of Queenland. All rights reserved. The SML Technical Report Series is                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| published by Sun Microsystems Laboratories, of Sun Microsystems, Inc. Printed in U.S.A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Unlimited copying without fee is permitted provided that the copies are not made nor distributed for direct commercial advantage, and credit to the source is given. Otherwise, no part of this work covered by copyright hereon may be reproduced in any form or by any means graphic, electronic, or mechanical, including photocopying, recording, taping, or storage in an information retrieval system, without the prior written permission of the copyright owner.                                                                                                     |

| TRADEMARKS Sun, Sun Microsystems, the Sun logo, Solaris, Java, JVM, and Java HotSpot are trademarks or registered trademarks of Sun Microsystems, Inc. in the U.S. and other countries. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. in the U.S. and other countries. Products bearing SPARC trademarks are based upon an architecture developed by Sun Microsystems, Inc. UNIX is a registered trademark in the United States and other countries, exclusively licensed through X/Open Company, Ltd. |

| For information regarding the SML Technical Report Series, contact Jeanie Treichel, Editor-in-Chief <jeanie.treichel@eng.sun.com>.All technical reports are available online on our Website, http://research.sun.com/techrep/.</jeanie.treichel@eng.sun.com>                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Experience in the Design, Implementation and Use of a Retargetable Static Binary Translation Framework**

Cristina Cifuentes

Sun Microsystems Laboratories

Palo Alto, CA 94303, USA

cristina.cifuentes@sun.com

Mike Van Emmerik The University of Queensland Brisbane QLD 4072, Australia emmerik@itee.uq.edu.au

Norman Ramsey

Division of Engineering and Applied Sciences

Harvard University, Cambridge, MA 01238, USA

nr@eecs.harvard.edu

Brian Lewis\*

Sun Microsystems Laboratories

Palo Alto, CA 94303, USA

brian.lewis@sun.com

# 1 Introduction

Binary translation, the process of translating binary executables,  $^1$  makes it possible to run code compiled for a source (input) machine  $M_s$  on a target (output) machine  $M_t$ . Unlike an interpreter or emulator, a binary translator makes it possible to approach the speed of native code on machine  $M_t$ . Translated code may run more slowly than native code because low-level properties of machine  $M_s$  must often be modeled on machine  $M_t$ . For example, the Digital Freeport Express translator [Dig95] simulates the byte order of the SPARC(R) architecture, and the FX!32 translator [Tho96, HH97] simulates the calling sequence of the source x86 machine, even though neither of these is native to the target Alpha architecture.

Binary translation techniques aim to translate the code (i.e., image) of an executable from one machine to equivalent code for another machine. Although it is not difficult to translate most

<sup>\*</sup>Now at Intel Microprocessor Research Labs. Email: brian.t.lewis@intel.com

<sup>&</sup>lt;sup>1</sup>In this document, the terms *binary executable*, *executable*, and *binary* files are used as synonyms to refer to the binary image file generated by a compiler or assembler to run on a particular computer.

machine instruction sequences from one machine to another, other considerations make the task difficult in practice. For example, binary code often mixes data and instructions in such a way that they cannot be distinguished. This problem is exacerbated by indirect or indexed jumps, where the target address of the jump may be hard to determine statically, even though it will be known at runtime. Further, some older operating systems did not provide systems programmers with an ABI (application binary interface) for low-level system calls, instead inviting application writers to directly access devices and system facilities, bypassing the operating system. These and other problems are common to binary-code manipulation tools such as disassemblers and decompilers. The static parsing of the machine instructions in a binary must be partially incomplete given its equivalence to the halting problem [HM79] and hence it is undecidable in general. Nevertheless, for binary translation purposes, this does not mean that the problem cannot be solved. In fact, given that the translated binary must be executable, information that cannot be determined statically will be available dynamically, and can be used by a runtime translator or an interpreter that operates at runtime to decode the instructions.

Problems that are specific to binary translation are due to its multi-platform nature: there is a need to address the differences between source and target architectures (e.g., CISC vs RISC); the endianness of the machines (e.g., little vs big); machine-dependent issues (e.g., delayed branches and register windows on the SPARC architecture); and compiler-generated idioms. As well, there are differences in operating system services and graphic subsystem calls—these are the hardest to address. Previous work reported in the literature suggested that a new binary translator must be hand-crafted for each pair of supported platforms due to machine dependency constraints.

In 1996 we started developing ideas and a framework for experimenting with such binary translation ideas. The University of Queensland Binary Translation (UQBT) project started at the University of Queensland, Australia, under the direction of Cristina Cifuentes. It was prompted by colleagues at Sun Microsystems Laboratories, who suggested the possibility of working with binaries and transforming them into binaries for another machine. Norman Ramsey and Mike Van Emmerik joined Cristina in shaping the project, Norman from a design point of view and Mike from an implementation point of view. During 2000-2001, the project became joint work with Sun Microsystems Laboratories. Brian Lewis joined this effort and worked on various back ends.

Experience with a prior binary-manipulation project had shown that most users understand little about the manipulation of binaries: they just want tools, and are rarely interested in knowing about the tool's internals or its data representations. Just as compiler technology has matured to the point of having retargetable compilers that can perform code generation for a variety of machines, we thought it was time to start understanding how to make binary-manipulation tools retargetable, for both source and target machines. Our focus was on static translators, hence the UQBT framework is a static binary translation framework.

We therefore set the following goals for the project:

- to understand what aspects of instruction representation and semantics are needed to perform binary translation,

- to write those aspects as formal machine descriptions,

- to derive components of binary translators from those descriptions,

- to understand how to implement existing machine-dependent analyses on a machine-independent RTL (register transfer) representation,

- to understand which of these analyses can be made machine-independent, and how, and

- to develop a framework for experimentation with binary manipulation ideas.

It is clear that an "all purpose" binary translator is very hard to develop, therefore some bounds for the research were established.

To keep things simple, *translation was limited to user code* (i.e., applications programs), not kernel code or system calls (i.e., systems programs), or dynamically linked libraries (as these are sometimes written in assembly code and often closely resemble systems programs). Note that this approach is not limiting; Digital used it for their FX!32 hybrid translator for x86 Windows 32-bit binaries on Alpha [HH97].

We worked within the context of a *multi-platform operating system*, the Solaris(TM) environment in particular, which runs on the SPARC and x86 platforms. Similar ideas work on other multiplatform OSs such as Linux and Windows NT. We also experimented with cross-OS translations where the two OSs were similar in nature; for example, Solaris and Linux environments. We have successfully translated (Solaris,SPARC) binaries onto (Linux,x86) binaries, provided the same runtime libraries were available in both systems.

The UQBT framework is our answer to the above goals. The framework consists of 89 C++ files, 77 header files, 40 specification and matching files, and numerous configuration and regression testing files. Users can instantiate translators out of the UQBT framework by configuring the system for a given pair of source and target machines. We instantiated 8 different translators, with time varying from 3 staff-months to 12 staff-months, as specifications or APIs must be written for each. One of our goals was to reduce the amount of retargetting work needed when supporting a new machine (whether source or target), by supporting machine-independent analyses wherever possible.

| Issues              | SPARC          | Pentium        | mc68328         | PA-RISC        | ARM            |

|---------------------|----------------|----------------|-----------------|----------------|----------------|

| Architecture        | RISC           | CISC           | CISC            | RISC           | RISC           |

| Endianness          | both           | little         | little          | big            | both           |

| Branching           | delayed        | non-delayed    | non-delayed     | delayed        | non-delayed    |

| Parameter pass-     | registers then | stack (regis-  | stack           | registers then | registers then |

| ing                 | stack          | ters possible) |                 | stack          | stack          |

| Stack grows         | low memory     | low memory     | low memory      | high memory    | low memory     |

| Float ops depend    | no             | yes            | no              | no             | no             |

| on int instructions |                |                |                 |                |                |

| Fixed pointers      | frame ptr      | frame ptr      | frame ptr,      | frame ptr      | frame ptr      |

|                     |                |                | global data ptr |                |                |

Figure 1: Main Differences Between Architectures Used

Figure 1 shows some of the differences between the machines our 8 translators supported. Differences between the architectures are summarized in terms of their instruction set (i.e., CISC or RISC), their endianness, the delayed or otherwise branching support, the locations used for parameter passing at procedure call boundaries, the direction the stack grows towards (i.e., low or high memory), whether floating point operations rely on integer instructions to obtain a result, and the types of fixed pointers that are commonly used in programs for those machines.

The UQBT framework is suitable for experimenting with binary manipulation; it is not a production system and was never designed to be one. Several undergraduate and some postgraduate students have worked on the system.

This paper is structured in the following way. §2 describes the UQBT framework and its intermediate code representations. §3 explains how users can instantiate translators out of the framework. §4 gives our experiences with the instantiation of new front ends and back ends for the UQBT framework. §5 discusses our lessons learned: what worked well, what did not, what was missing, and what we would do differently if doing it over again. Lastly, some conclusions close this paper.

# 2 The UQBT Framework

The UQBT framework was designed with retargetability in mind. We were interested in supporting binaries for different input and output machines, so we made the framework retargetable for both. In our notation, we refer to the input machine as the *source machine*  $(M_s)$ , and the output machine as the *target machine*  $(M_t)$ . The framework was designed so that users could instantiate new translators out of the framework for their source and target machines of choice, to run on a *host platform*.

As with a compiler, a binary translator can be viewed as composed of two main parts, a front end and a back end, only here both parts deal with machine-specific information. In a binary translator, the front end translates machine-specific information into an intermediate representation suitable for analysis. The back end translates that intermediate representation down to machine code for a target machine.

To make a compiler retargetable, two approaches are most often used. The most common approach makes use of machine description files that describe machine instructions, including some semantic features at times, to support compilation or optimization of code. Examples of this approach include the GNU compiler suite [Sta93] and the VPO optimizer [BD88]. With both of these systems, some modules are machine-independent, and machine-dependent modules need to be written by the compiler/optimizer writer. The amount of code to be written varies depending on the complexity of the instruction set and the optimization support wanted. The second approach makes use of abstract classes describing the machine-independent information that is needed to analyze code. This object oriented approach relies on subclassing to support other machines, and new features of a machine that do not exist in other machines are added only to the machine's subclass. In the event that a new feature is available in multiple machines, that feature can be

supported in a higher-level class. The abstraction does not need to be implemented using an object oriented language per se, the abstraction can be described in non-object oriented programs in the form of an application programmer interface (API). Programs such as the X toolkit have shown that extensibility is possible when using an API approach.

In the UQBT framework, the first phase of the project concentrated on the front end, and we aimed to support retargetability by describing machine and operating system conventions. The second phase of the project concentrated on the back end. We placed less emphasis on the use of machine descriptions (though we still used them at times), and placed more emphasis on using an abstract API to structure the back end translation process so we could experiment with multiple back ends. We first explain the intermediate representation we used, then explain the front and back ends.

## 2.1 Intermediate Representations

As with compilers, binary translators make use of several intermediate representations of the code to be translated. A program is a collection of procedures.<sup>2</sup> A procedure is represented by its control flow graph and instructions. Instructions are represented by one of two intermediate representations. A control flow graph is a series of basic blocks that describe transfers of control in a procedure. Individual basic blocks contain information about the instructions in that block.

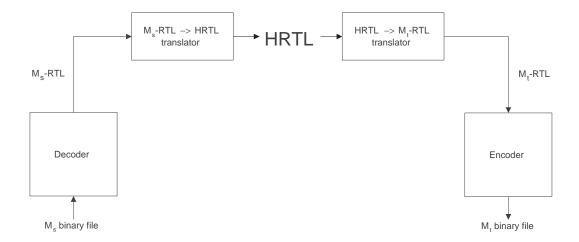

Two main intermediate representations for the code of the program are used in the framework: a low-level representation based on register transfers called RTL, and a high-level, machine-independent representation called HRTL. A high-level view of a binary translator based on these two representations is shown in Figure 2. The decoding stage translates the code in the source binary file into RTLs for that source machine  $M_s$ . An analysis stage then translates those  $M_s$ -RTLs into HRTLs, by abstracting away information from the underlying machine. Once we have HRTL code, standard compiler back end techniques are used to generate binary code for the target machine  $M_t$ . An analysis stage translates the HRTL code into RTLs for the target machine, ensuring the  $M_t$ -RTLs represent instructions of the target machine. Finally, the encoding stage translates the machine-specific  $M_t$ -RTLs into binary code for the target machine.

#### 2.1.1 RTL

A register transfer list (RTL) is a collection of sequential effects. Each effect has the form 'location := expression', and the expression is always evaluated without side effects, so that all state change is explicit. RTL expressions are represented as trees, the leaves of which refer to constants or to the values contained in locations. Note that although the tree leaves refer to locations, the values themselves are not necessarily calculated, only the location is indicated. The internal nodes of the trees are 'RTL operators'. The locations available are an infinite number of registers r[.] and infinite memory r[.]. Register locations can be named, for example, r[.] can represent the 1-bit overflow flag. In this paper, we use the symbol r[.] to denote locations.

<sup>&</sup>lt;sup>2</sup>We use the term procedure to represent a code chunk that is invoked by a call in the program. The code chunk may or may not return to its parent caller, and it may or may not return a value as the result of the call operation.

Figure 2: Intermediate Representations and a Block-level View of the UQBT Framework

To illustrate this, the following is an ASCII representation of an RTL representing the effect of the SPARC architecture andcc instruction. This instruction has an i field which determines whether the instruction takes a register or an signed immediate value as its second operand:

This RTL does a bitwise AND of the contents of register r[rs1], either with the contents of register r[rs2] or with a signed immediate value (simm13). The symbol \* denotes a value and the symbol ! stands for sign extension. This result is stored in register r[rd], and it is also used to set two of the four condition codes. The other two condition codes are set to zero by the instruction.

RTLs are complex and detailed. Machine descriptions make use of the 'superoperator' technique [Pro95] to simplify the description of condition code effects. For example, we define a superoperator LOGICAL for the SPARC architecture such that LOGICAL(X) stands for

```

$NF <-- bit ((X) < 0);

$ZF <-- bit ((X) = 0);

$OF <-- 0;

$CF <-- 0

```

Register locations carry with them typing information in the form of a (type, size, sign) tuple. The type is one of four low-level, machine-like, types; namely, integer, float, pointer to data or pointer to code. The size is the number of bits of the type, typically from 1 to 64. The sign is a boolean denoting whether the location is signed or not (integer types only).

An 'RTL language' is defined by a collection of locations and operators. For binary translation, a suitable RTL language is defined by taking the union of locations on machines  $M_s$  and  $M_t$  and the

union of the operators used in the descriptions of machine  $M_s$  and  $M_t$ . The 'machine X invariant' defines a sub-language of RTLs called the X-RTLs; an RTL is an X-RTL if and only if it can be represented as a single instruction on machine X; i.e., there is a 1:1 correspondence between assembly instructions for machine X and X-RTL instructions.

#### 2.1.2 HRTL

The high-level register transfer language, HRTL, is a collection of instructions that affect the state of locations. The language is defined by a set of operators and instructions. The main aim in the design of the HRTL language was to be able to express code semantics in a way that was machine-independent. As such, translations to the HRTL language require analyses that abstract away the peculiarities of individual machine instruction sets. For example, features such as the next PC register in architectures that support delayed branching semantics, are not exposed in the HRTL representation; such code needs to be transformed into equivalent code that does not make use of the next PC register.

HRTL instructions operate on locations. As per RTL, there are an infinite number of registers (\$r[.], which may be named, e.g., \$X) and an infinite memory (\$m[.]). Further, HRTL has an infinite number of variables (\$v.), which are locations that can hold actual and formal parameters of procedure calls. Both register and variable locations carry typing information.

HRTL supports assignments of the RTL form 'location := expression', as well as higher-level instructions such as conditional, unconditional and computed jumps of the form 'jump [cond expression] list of locations>', procedure call of the form 'call location (dist of variables>)', and returns of the form 'return location'. Assignments also support the form 'location := call location (of variables>)'.

As an illustration, the following is an ASCII representation of a HRTL that represents the SPARC architecture and cc %03,64,%g1 instruction after transforming the sample SPARC-RTL of  $\S2.1.1$ . In the example, %03 is represented by register \$r[10] and %g1 by register \$r[1]. Note that condition code analysis will either determine that assignments to condition codes are dead (and hence remove them) or move the effect of the condition code assignment to another HRTL that makes use of a conditional expression. In this example, the condition codes were found to be dead.

```

r[1] \leftarrow and (*r[10], 64);

```

A more interesting example is the HRTL representation of the SPARC architecture call instruction, which stores the return program counter address in register %07 (i.e., register \$r[15]). The SPARC-RTL for this instruction is

```

$r[15] <-- *$pc;

$pc <-- *$npc;

$npc <-- *$r[15] + (4 * disp30);</pre>

```

The SPARC architecture call instruction with displacement 0x4318, invoked at program counter location 0x00010B20 is transformed into the following HRTL instruction

```

call 0x00021780;

```

where  $0 \times 00021780$  is equivalent to the computation of  $0 \times 00010B20 + (4 * 0 \times 4318)$ .

## 2.1.3 An Example

In order to give readers an idea of the implications of the HRTL representation, we show, without going into low-level details about the translation process, how a series of SPARC-RTLs and Pentium-RTLs end up being represented in HRTL. Our sample C language statement is from the Fibonacci program, where the following statement invokes the fibonacci procedure fib with the argument number and stores its result in variable value

```

value = fib (number);

```

The unoptimized SPARC-assembly code for the C language statement is

which corresponds to the following SPARC-RTLs. Note that only control transfer instructions make explicit changes to the \$pc and \$ppc registers.

The same C language statement is represented by the following Pentium-assembly instructions

which corresponds to the following Pentium-RTLs

```

$r[24]

<-- *$m[*$r[29]-4]

// load parameter

$r[28]

<-- *$r[28] - 4

// put it on the stack

$m[*$r[28]]

<-- *$r[24]

<-- *$r[28] - 4

$r[28]

// call fib

$m[*$r[28]]

<-- * pc + 5

<--0 \times 8048960

$pc

$r[28]

<-- *$r[28] + 4

// fix stack frame

$r[24]

<-- *$r[24]

$m[*$r[29]-8] <-- *$r[24]

// assign return value

```

After transformational analysis, the HRTL code obtained for both RTL representations follows

```

HRTL (SPARC) HRTL (Pentium)

$v0 <-- *$m[*$afp+100] $v3 <-- *$m[*$afp+4]

$v0 <-- call fib (*$v0) $v4 <-- *$v3

$m[*$afp+96] <-- *$v0 $v3 <-- call fib (*$v4)

$m[*$afp] <-- *$v3

```

The \$afp named location is the abstract frame pointer, which points into the local memory stack for the procedure. It is clear that in both cases the code fetches a value from the local stack into a variable, then it passes the variable's value to the procedure call fib, which returns a result that it then places in another variable. That result value is then stored onto the local memory stack. Simple forward substitution would make both codes have the same number of HRTL instructions; that step is a simple optimization step left to the back end.

This example illustrates the benefits we found from having a high-level, machine-independent representation. It is suitable for generating native code for a target machine in an optimal way, instead of emulating features of the source machine. In this case, we did not have to directly emulate the SPARC architecture \$pc or \$npc registers, which would have required us to update the equivalent of their values after every Pentium instruction in, most likely, two of the scarce Pentium registers.

The Appendix shows a complete example for a translation of a Pentium-compiled recursive fibonacci program to the SPARC architecture.

## 2.2 Front End

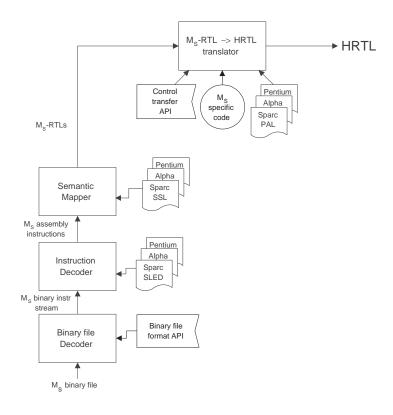

The UQBT front end translates a source binary file into HRTL. Figure 3 provides a dataflow view of the transformations of the code to arrive at the HRTL representation. In this figure, boxes represent reusable components of the framework (some require some code to be written), document files represent specifications, notched boxes represent APIs, and the circle represents machine-specific code that needs to be written by the binary translator writer.

In short, the UQBT front end provides a binary file decoder which reads an instruction stream from an input binary file. This instruction stream is parsed into a sequence of source machine

Figure 3: The Retargetable Front End of the UQBT Framework

instructions using a description of the syntax of machine instructions for that machine. A semantic mapper then translates each source machine instruction into a sequence of source machine-specific RTLs ( $M_s$ -RTLs) using a specification of the semantics for the source machine's instructions. The resulting  $M_s$ -RTL stream is analyzed by an  $M_s$ -RTL to HRTL translator using control transfer information, procedural conventions and other information.

The specifications and APIs capture information about the machine or the operating system used by the source binary file. These specifications and APIs support retargetability of the front end, and we briefly describe them below, prior to describing the parts of the front end itself. Note that for historical reasons, these descriptions end up being implemented in different files that use different languages; conceptually, these descriptions could be part of the one machine-description file. The languages we use are described in the literature, and we give references for them below.

- Machine-specific information: a computer architecture's properties are described using three kinds of information. These are 1) the syntax of its instructions (their mnemonics, operands, and instruction bitfields); 2) their semantics; and 3) a description of its control transfer instructions. The following specifications and APIs provide this information:

- SLED (Specification Language for Encoding and Decoding) specifications allow users to specify the mapping between the binary and the assembly representation of a machine instruction set, as well as the machine's registers and names for those registers [RF97].

- SSL (Semantic Specification Language) specifications allow users to specify the mapping between assembly instructions and their equivalent RTLs, to name new registers and declare overlaps, to define superoperators in the form of macros for commonly set condition codes, and to specify the fetch-execute cycle for the machine [CS98].

- Control transfer API allows users to support the identification of instructions that perform transfers of control (unconditional jumps, conditional jumps, calls, and returns).

- OS-specific information: conventions used by the operating system are described using two kinds of information: the procedure calling conventions and the format of the binary file. These conventions are supported using the following API and specification:

- The binary file format API allows users to load and decode binary files and hides details about the binary's internal representation. This API assumes that there is at least one entry point into the program, that code and data sections exist with known addresses, and that there may be a symbol table (which is used for names if it exists), [CERL01] at Chapter 5.

- PAL (Procedural Abstraction Language) allows users to describe the conventions dealing with procedures; such as, calling conventions, parameter passing conventions, storage conventions for local variables, and callee stack frame information [CS00].

#### 2.2.1 The Front End Modules

The front end is composed of a series of conceptual modules that transform the source input text stream into a high-level representation. This series of modules is briefly described herein; more details are available in the UQBT documentation [CERL01].

#### Binary file decoder

The binary file decoder decodes the source binary file into an internal UQBT representation that supports the binary file format API. All text and data sections are copied "as is" into memory and information about the binary file is stored in an internal representation.

The binary file decoder makes the entry point into the text section available, as well as the main entry point into the user-written part of the program (if available and detectable).

#### **Instruction decoder**

The instruction decoder disassembles the (text/code) instruction stream starting at the main entry point. The disassembly matches the binary representation of instructions into equivalent assembly instructions, as specified in the machine's SLED file. This support is done using the New Jersey Machine Code toolkit's matching files [RF97].

The algorithm used is the standard reaching algorithm from a given entry point [SCK<sup>+</sup>93, CG95]: Starting at an entry point, follow the program's path until a transfer of control is met. When a

control transfer implies more than one target address, follow one of the addresses and place the others on a queue to be processed (i.e., these are new entry points). When a path ends, follow another path from the queue to be processed, until no addresses remain in the queue.

Note that since the translation is done statically, it is not always possible to know a priori the targets of computed transfers of control such as indirect or indexed jumps or indirect calls. Analysis of such cases is described in §2.2.3, which allows for better coverage when decoding the text section; however, it cannot guarantee complete code coverage.

### **Semantic mapper**

The semantic mapper maps assembly instructions into RTLs for the source machine, effectively generating  $M_s$ -RTLs for the source binary file's code section. The RTLs are provided by the SSL specification for that machine. This step is done immediately after an assembly instruction is matched; that instruction is transformed into a list of register transfers and stored in this representation.

#### M<sub>s</sub>-RTL to HRTL translator

The M<sub>s</sub>-RTL to HRTL translator is the key module in the framework that allows us to achieve machine independence in representating the program's code. This module transforms RTL instructions into HRTL instructions by supporting an informal control transfer API, performing analyses on procedural information (such as parameters, locals and return locations), and adding any extra hand-written code to support peculiarities of the source instruction set. The latter peculiarities include delayed branches on the SPARC architecture or floating point stack-based instructions on x86. These are explained in §2.2.2.

Control transfer. Support for the control transfer API allows us to transform RTL instructions into very simple HRTL instructions that do not take the required parameters yet. For example, a sequence of RTL instructions can be transformed into a call HRTL instruction even though no analysis has been performed to determine the parameters to the call instruction per se. This intermediate state in our HRTL representation is what we refer to as I-RTL. In a similar way, jumps and return instructions are transformed into I-RTLs and then analyzed for operands.

**Procedural abstraction.** The procedural abstraction analysis makes use of PAL descriptions to determine the parameters passed to a procedure. This interprocedural analysis is performed based on a liveness analysis on locations that are valid parameter-locations at the caller and callee sites. We also transform the code in each procedure so that references to the frame pointer are transformed into references to an abstract frame pointer (\$afp), which is a conceptual pointer to the end of the stack frame (usually, where the stack pointer points after the callee prologue). The analysis keeps track of changes to registers relating to \$afp, usually the stack pointer, and often also a frame pointer register. It knows the relationship

between \$afp and these registers at every instruction, and replaces references to these registers with \$afp plus or minus a constant.

The advantage of using a conceptual frame pointer such as \$afp is that we do not need to emulate a moving stack pointer on the target machine, which may not be efficient; for example, RISC machines do not have push instructions, and simulating them is very inefficient. Instead, we generate code that is much more in harmony with the target architecture. An array of bytes is generated to handle these source stack frame locations, with the array name becoming the equivalent location to \$afp (or array name + size for machines where the stack grows upwards). A complete description of these analyses is available in [CS00].

Note that no changes are made to the data of the source program, that is, the data and all references to them remain unchanged.

Once a HRTL representation of the program has been obtained, binary translation-specific optimizations can be performed on the representation. For example, when translating to a machine with different endianness, the common technique is to perform byte swapping of data after each load and before each store instruction. An analysis at the HRTL level may help reduce the number of byte swaps required at each load and store from memory. This type of optimization, though feasible, was not implemented in the UQBT framework.

## 2.2.2 Machine-specific Analyses

The  $M_s$ -RTL to HRTL translator normally includes code that is written for a particular machine to perform code transformations to remove that machine's peculiarities. In our experience, for every source machine we supported, we had to add special analysis to transform away some feature of that machine. The following lists some of these machine features.

#### **SPARC**

The SPARC architecture supports delayed branches: the instruction following a branch—the delay slot instruction—is executed before the transfer of control reaches the branch's target instruction. The processor keeps track of instructions by using an extra program counter register, the next program counter or \$npc, which is updated by all branching instructions as well as at each iteration of the fetch-execute cycle for non-branching instructions. The \$npc register is a SPARC-specific register. When doing binary translation, unless assignments to the \$npc register are transformed away (in effect removing the register from the code), it would be necessary to emulate that register and all assignments to it. For this purpose, we developed a transformational analysis to remove delayed branches [CR02]. The technique is general enough to be used on any processor with delayed branches such as the MIPS, SPARC, and PA-RISC processors.

#### **Pentium**

The Pentium architecture supports floating point instructions using a different set of registers than those used by integer instructions. These floating point instructions originated from a time when they were implemented by a separate math coprocessor: the 80x87 series, e.g., the 80387 provides floating point support for the 80386 processor. These separate floating point instructions, registers, and conventions persist despite the fact that from the 80486 processor onwards, floating point support has been integrated onto the processor chip itself.

Because of this, floating point condition codes must be moved into integer condition code registers (via the \$ax register) in order to perform branching. There are no branch instructions based on floating point condition codes; they would have been difficult to support since the branch processor and floating point condition codes are in separate chips. In fact, later Pentiums (from the Pentium Pro onwards) have a set of compare instructions that affect the integer flags. Most compilers do not take advantage of these instructions, since they are not available on earlier processors.

On the Pentium architecture, floating point instructions make use of an 8-register stack. This register stack can either be accessed as an actual stack or indexed directly as an array relative to the top of stack. Since we do not want to emulate a floating point stack in translated code, we transform the code to use a conventional "flat" register model. Instead of instructions that implicitly use the top and next of stack as operands, the transformed code refers to actual registers such as \$r[39]. We had to take into consideration all the tricks commonly used to implement floating point compares. For example, some compilers would store the floating point flags to register \$ax, then move register \$ax to the integer flags, before performing an integer branch. Others would avoid the movement from register \$ax to the flags (a slow, "non pairable" instruction) using code like this

Note that the actual branch condition (branch if zero) in the last instruction bears no relationship to the floating point comparison that this code sequence implements (floating point greater than). Hence there must be a good deal of pattern matching in the Pentium front end to convert these idiomatic sequences to high level branches. The above code would be converted to the following HRTL code by a UQBT translator<sup>3</sup>

```

08049f28 *32* v7 := b

*32* v6 := a

08049f2b 	 JCOND ((v6 > v7):<32f>) 0x08049f0c

```

$<sup>^3</sup>$ UQBT's HRTL ASCII representation does not use \$ or \* to denote locations or content of a location. The \*32\* notation denotes the size in bits of the assignment attached to that line. The <32f> notation denotes a (size,type) tuple for a location or expression. JCOND stands for conditional jump instruction.

Note that the x86 details of copying from the floating point flags to \$ax, the AND instruction, the immediate value 41H, and the branch if zero are replaced by a high level comparison between two floating point variables. The generated C code becomes

```

if (v6 > v7) goto L10;

```

#### 68328

The MC68328 architecture is used in the Palm Pilot device. The PalmOS makes use of a dedicated register (\$a5) to access global data in the data section. The global data pointer acts much like a frame pointer. In UQBT, instead of emulating the global data pointer register and each of its updates, we extended the frame pointer removal analysis already done by the M<sub>s</sub>-RTL to HRTL translator in order to transform the pointer into an abstract global pointer (\$agp). The \$agp abstract register is deemed to point to the start of a global array of bytes (compare this with the \$afp register, which points to the start of the array of bytes that represents a procedure frame). This allows us to generate target code that does not depend on the PalmOS initializing the \$a5 register before the start of main. In some systems, a global data pointer actually points to the middle of the data so that positive and negative offsets can be used to double the register's reach. In this case, the actual register will contain a constant offset from the start of the global data array.

In order to specify the behavior of a global pointer in the PAL language, we introduced a special keyword GLOBALOFFSET, which is a constant for any particular input file but can vary from one input file to another. Our binary loader class has a method called GetGlobalOffsetInfo that returns the total size of the global data array, and another value that is useful for specifying the global data behavior. In the case of the PalmOS loader, this is the offset from the start of the global data to where the \$a5 register points. Other loaders can return different information if desired; of course, the loader and the PAL file must agree on what meaning is attached to the GLOBALOFFSET value. For example, the following appears in the PalmOS PAL specification<sup>4</sup>

```

GLOBAL ABSTRACTION

%a5 -> %agp + GLOBALOFFSET

```

This specification says that the \$a5 register points a constant distance into the global data array, by an amount GLOBALOFFSET that is known to the binary file loader. An example of generated C code that makes use of an %agp reference is as follows

```

*((int8*)((_globals)+(57)))=0;

```

#### **PA-RISC**

The PA-RISC architecture supports delayed branches. As a result, the delayed branching transformational analysis developed for the SPARC architecture was reused in the PA-RISC front end by

<sup>&</sup>lt;sup>4</sup>PAL uses % to denote named registers.

instantiating a new version of the algorithm to support its instruction set. It is interesting that the PA-RISC has three classes of delayed branches different from those in the SPARC architecture. We were able to support these using the algorithm although this was not obvious at first. Details on this transformation are available in a technical report [CR02].

The PA-RISC instruction decoder makes significant use of guarded assignments. In order to make the code more readable (and to allow higher level analyses to recognise certain expressions), it is necessary to do extra simplification of PA-RISC assignments (including guards), and also to do forward substitution within the RTLs of each instruction.

## 2.2.3 Other Instruction Decoding Analyses

In a static translator, coverage of the source program's code section is important, since translating more code statically minimizes the need for a runtime interpreter to execute untranslated pieces of code. Heavy reliance on runtime interpretation hampers the use of translated programs, as interpretation is slow and users want their programs to execute without perceivable pauses.

In order to improve the coverage of decoding achieved by the standard decoding algorithm, we implemented an analysis to recover the targets of computed jumps when such jumps represent switch statements in C and similar languages. We also implemented a speculative decoding algorithm to traverse the remaining sections of the code section that had not been decoded yet, and determine if they represent valid code that could be translated statically. Descriptions of these two techniques follow.

We note that these techniques considerably increase static translation coverage, but they do not guarantee complete coverage. The Digital VEST and mx translators made use of backward symbolic execution to resolve as many computed branch targets as feasible [SCK+93]. In general, this is a hard problem to solve, although extensive testing and taking advantage of commonly-generated compiler idioms increases coverage. However, we also note that code written back in the 1980s and early 1990s was mainly written in the C language and therefore was not object oriented and did not support dynamic dispatching of procedures (methods). Dynamic dispatching is implemented by C++ compilers using a virtual method table and an indirect call based on a register value. That register value is normally only determined at runtime based on the actual class of the method being invoked, so these programs require further analysis to increase their static translation coverage. Similar techniques can be used to recover the targets of virtual method calls [TC02].

#### **Recovery of Computed Jumps**

The standard method of decoding machine code involves following all reachable paths from the entry point [SCK<sup>+</sup>93, CG95]. This method does not give a complete coverage of the code space in the presence of indirect transfers of control such as indexed jumps and indirect calls. A common technique used to overcome this problem is the use of patterns. A pattern is used for a particular compiler to deal with the particular code sequences that compiler, or family of compilers, generates

for a table lookup. This technique is used often since most tools deal with only a particular set of compilers; for example, TracePoint just processes Windows binaries generated by the Microsoft C++ compiler [Tra97]. In the presence of optimized code, patterns do not tend to work very effectively, even when the code is generated by a compiler known to the pattern recognizer.

We developed a machine-independent technique to recover computed jumps. This technique was developed after studying code generated by C, C++, Modula, and Pascal compilers, and was tested on both SPARC and Pentium architectures using moderately sized programs (e.g., the SPEC 1995 benchmark suite).

The technique can be summarized as follows. At an indexed jump instruction, perform backwards slicing of the code up until either the start of the procedure containing the indexed jump or when the terminating conditions for a computed jump slice are met. Copy propagate values in the slice's RTL representation and remove any dead instructions from the slice. Transform the remaining instructions to a normal form and compare against the three normal forms documented in [CE01]. If a match exists, the bounds of a jump table can be determined, as well as the size and location of the jump table, and the form of its contents (whether addresses or offsets). In this case, replace the indexed jump by a HRTL computed jump having the appropriate target addresses. Finally, follow each target address to decode more code. This last step significantly increases code coverage.

## **Speculative Decoding**

To get better coverage when decoding the code section, particularly for binaries that were compiled using compilers for object-oriented languages which use virtual tables, we implemented a crude but effective speculative decoding technique that was used after the standard decoding phase finished.

The technique is simple. For every gap in the code section where there are untranslated bytes, we decode the bytes speculatively as if the gap was a procedure in the source binary. If an illegal instruction is encountered, the translated code is discarded, and speculation continues at the next gap.

The source and target code addresses of all translated procedures, including these "speculative procedures," are put into a table. This essentially creates a forest of translated code trees. The table is used at runtime to handle indirect branches through registers and virtual method calls.

To support object oriented programs, register calls are translated into a call to a small runtime procedure. That procedure, in turn, calls a C language function to look up the address in the table and jump to the target address if found. A simple binary search is used. Note that the address looked up for a register call will be for a procedure in the *source* binary; the procedure table is used to find the address of the corresponding procedure in the translated (*target*) binary. The machine code of the source binary is needed, in case the target of the register call is not found in the table of (source, target) address pairs. This would mean that despite the speculative decoding, not all source functions were found and decoded. All live potential parameter locations are passed to the function handling the register call.

This simple technique was found to work reasonably well, although in some cases overlapping procedures were generated, which wasted some space in the target binary.

## **Helper Functions**

The runtime library for the SPARC architecture, as well as that of other architectures, provides some architecture-specific functions to perform simple arithmetic functions efficiently. For example, the .umul function performs an unsigned multiplication. We dubbed these functions "helper functions."

Helper functions have a predefined semantics and their parameters are known and fixed in number. We search for these functions during the decoding phase and, when matched, replace them with the helper function's semantics in terms of RTLs. For example, we replace a call to .umul by the RTL expression r[8]\*r[9].

### 2.3 Back End

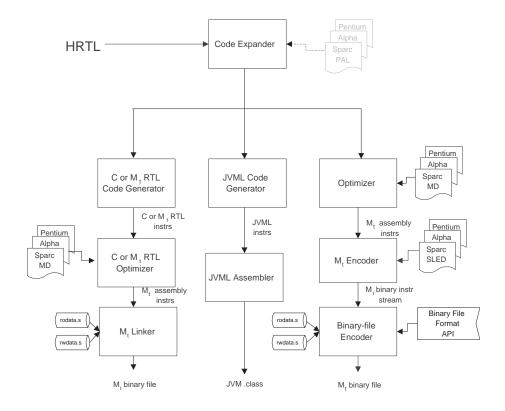

We experimented with different types of back ends to try to determine the benefits of one approach over another. In 1999, the UQBT framework initially supported a simple C back end that used the C compiler as a macro assembler. This allowed us to have our first complete binary translator for several different source and target machines, and we instantiated four different translators at that time. Over time, we added additional back ends and Figure 4 shows the different kinds of back ends that we eventually built. We supported commonalities between these back ends using an abstract class that we called the code expander. In its present form, the code expander does not make use of PAL specifications for determining calling conventions, but rather makes use of a predetermined one.

#### 2.3.1 The C Back End

The C back end was the first back end we wrote for the UQBT framework. The idea behind it is simple: translate HRTL code into low-level C code, without attempting to recover any "high-level" control flow structure (no do, while or for loops). All control flow is in the form of gotos. The binary translator does not "understand the data," but merely replicates the bit pattern changes that the source program performed. As a result, the generated C code does much casting of expressions between different types, and all memory references are of the form \*(<type>\*)<address expression>. Automatic (data) type coercion of the C programming language must be avoided. Actual conversion operations (e.g., sign extending of integers; converting from integer to floating point) is often only expressable in the C language using casts. Combined with the often redundant and copious parentheses, the resultant code is difficult for humans to read. In fact, there is an outstanding bug with the GNU gcc compiler, where a particularly "ugly" expression is handled incorrectly when optimized. Figure 5 illustrates some of the generated low-level C code.

Figure 4: Conceptual View of the UQBT Framework's Back End

For each procedure we generate one C language file, and for the whole program one makefile. Data sections are copied without modification into assembly files (using .byte statements) and a map file is generated to force the data sections to be loaded at the same virtual address as in the original source binary.

The generated code is then compiled using a C compiler (normally using GNU gcc or Sun Microsystems cc compilers) and then linked with the original data sections of the source program. Note, however, that some features such as endianness support require powerful macro support to implement efficiently, which in practice may limit the choice of target compiler to GNU gcc. The source binary's code section is optionally also copied to the target binary.

We found it necessary to keep an accurate record of the "current type" of an expression while generating its code. The reason for this is that the C compiler does the same thing, and it bases its decision on whether to emit conversion operations on the current type of operands. In some cases, the only way to tell the C compiler to emit code to perform a certain operation is to correctly cast the operands. An example is the right shift operation; the C operator for both arithmetic and logic right shift is >>; which instruction is emitted depends on the type of the operands. Thus, when a sub-expression of a given expression is computed, we take great care to specify the correct type for the sub-expression. For example, the only sub-expression in the floating point to integer expression ftoi(64,32,m[1000]) is \$m[1000], and its type is 64-bit float.

```

#include "uqbt.h"

int main(int v0, int v1) {

int v2, v3, v4, v5, v9, v10;

double v8;

union {

double d65;

struct {

float f34;

float f35;

} f;

} d65;

v3=67584;

v2=(v3) | (304);

v4= *((int *)(*(unsigned int *)&v2));

v5 = *((int *)((*(unsigned int *)&v2)+(4)));

v9=v4;

v10=v5;

d65.f.f34=*(float *)&v9;

d65.f.f35=*(float *)&v10;

v8=d65.d65;

d65.f.f34=*(float *)&v8;

*(int *)&d65.f.f35= *((int *)(((int*)(&v8))+(1)));

/* ... */

}

```

Figure 5: Sample Generated Low-level C Code.

Another challenge was the handling of overlapped registers. For example, the 32 bit Pentium register \$eax is overlapped by the 16 bit register \$ax and the 8 bit register \$al. In many architectures, single precision floating point registers overlap double precision registers. Our approach to this is to ignore the overlap in the internal representation (RTLs and HRTLs), and give the overlapped registers different register numbers. To handle the overlap, we emit C code that declares the overlapped registers as unions. Since this makes the code even more difficult for humans to understand, this declaration is done only when needed. An extra pass in the back end is used to find all registers used in a procedure.

#### 2.3.2 The JVML Back End

The bytecode for the Java(TM) programming language (i.e., the Java virtual machine language (JVML)) back end was written as an experiment in translating machine code to Java bytecodes.

We translated HRTL code into classfiles for the Java virtual machine (JVM(TM)),<sup>5</sup> using the Jasmin JVM bytecode assembler [Mey97]. The JVML back end operated much like the C back end but was more limited in what it could translate. It was single-pass and produced a bytecode assembly file by translating each HRTL procedure into the bytecodes for a Java language method. A postorder traversal of each HRTL's sub-expressions produced the stack-oriented JVM bytecodes for that HRTL.

The resulting class file made use of a compatibility library class that emulated the source platform's libraries on the target JVM platform. This library also included methods to support a limited subset of C's memory model. Memory was represented using a single large, pre-allocated Java language byte array memory. References to a data item at a particular address x were read from or written to memory[x]. The compatibility class contained a method that was called first when the translated program began execution. That method initialized the memory array by copying the program's command line arguments and the source program's bss and data segments into the appropriate array elements. malloc was implemented by a method that allocated a block of storage from memory then returned that block's offset. Pointer arithmetic done by the source program was implemented using arithmetic operations on memory offsets. Function pointers were not supported.

This experimental JVM back end was suitable for translating small numerical SPARC architecture binary programs. It supported 32 and 64 bit floating point and signed 8, 16, 32, and 64 bit integer types, but did not implement the entire C memory model. Overlapping registers were not supported. It also did not implement unsigned integers since these are not directly supported by the JVM. It would have been possible to add compatibility methods to support unsigned integers, but this was never done.

## 2.3.3 The RTL Back End

The RTL back end was an experiment at having more control over the types of optimizations that were applied to the generated code; control that was not available with the C back end as the C compiler would dictate what optimizations to use.

The idea behind the RTL back end was not only to have better control over the types of optimizations applied to the generated code, but it was also our feeling that interfacing at the RTL level would provide us with better target code, as instructions would be more easily expressible at the RTL level than through C language statements that include numerous type casts.

For our experiments, we used the Very Portable Optimizer VPO [BD88, VPO98]. An RTL interface to VPO was made available in 1999. This interface supports the SPARC, x86 and ARM architectures among others. VPO makes use of machine description files to describe the instructions of a machine. VPO implements a series of machine-independent optimizations and allows the user to write machine-dependent optimizations to support a new machine. We reused the existing machine descriptions and optimizations rather than writing our own.

<sup>&</sup>lt;sup>5</sup>The terms "Java virtual machine" and "JVM" mean a virtual machine for the Java(TM) platform.

Our RTL back end was mainly a translator of HRTL to  $M_t$ -RTL code (in VPO's RTL format), which was passed to the VPO retargetable optimizer through its RTL interface. The optimized code emitted by VPO was then linked with the original data sections to generate the final target binary.

### 2.3.4 The Object Code Back End

The object code back end was written as an experiment in interfacing with an optimizer at the object code level: i.e., it emits a binary executable directly, without any particular intermediate representation. This back end enables the use of any optimizer that can operate on an executable binary.

The object code back end translates HRTL code to  $M_t$ -assembly without performing any but the very simplest register allocation. It allocates all variables in memory, in the procedure's local stack, and emits loads and stores to those memory locations. It relies on the optimizer to do efficient register allocation. The back end encodes  $M_t$ -assembly instructions into their binary representation using SLED machine instruction descriptions and the New Jersey Machine Code toolkit's encoding routines [RF97]. We experimented with the use of this back end in conjunction with a proprietary SPARC architecture post-link optimizer.

## 2.4 Runtime Support

The UQBT back ends generate source code for the translated program in either the C, JVML or machine code languages, by providing a series of files (one per translated procedure); the data files in assembly language format; and a makefile to build the final target binary.

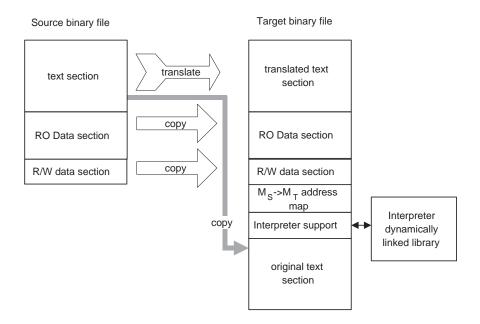

Figure 6 illustrates the components of the target binary. Basically, the source text section is translated into an equivalent text section, the read-only and read-write data sections are copied as is to the target binary, and several sections are added for interpretation support.

A static binary translator requires some runtime support in the form of an interpreter or dynamic translator to emulate those parts of the source program that could not be translated statically. In the UQBT framework, we provide for speculative decoding and recovery of jump tables as analyses that aid in achieving a greater coverage of translation of the source text section (see §2.2.3). However, no available static technique can guarantee full coverage of decoding of the text section for all input programs, therefore, interpretation support is needed in the generated target binaries.

A UQBT-generated target binary that requires interpretation support should add the following sections to the target binary: the source to target address mapping (to aid in determining when a piece of code has been translated); some basic interpretation support (to check for translated code that may be part of a pre-translated tree of code resulting from the speculative decoding analysis, or to invoke an interpreter); and the original (source) text section (for the interpreter to interpret instructions from this text section).

Figure 6: Internal Format for Source and Target (Generated) Binaries

We experimented with two different interpreters: a UQBT-RTL interpreter and a source machine instruction interpreter (emulator). The former interpreter was slow and not fully tested. The latter emulator worked well and was capable, for example, of running all SPEC 95 benchmark programs. Neither interpreter was fully integrated with the UQBT framework since we did not want to become dependent on them: one of our goals was to use analysis to avoid, as much as possible, relying on runtime support.

In principle, integrating an interpreter is relatively simple to do. However, it does require a map of source-to-target register locations. This is a mapping of source registers to the translated virtual (in memory) and physical (in target machine register) locations. Integrating a runtime emulator also requires support for determining when (i.e., at what instructions) it is safe to return to translated code. Safe points normally include the return from a procedure for example. At a safe point, the state of the translated program needs to be mapped based on the state of the emulated machine.

# 3 Instantiation of Translators

The UQBT framework supports the instantiation of different translators with specifications of the source and target machines. For example, to instantiate a SPARC to SPARC translator, the UQBT framework is configured to use specifications for the SPARC architecture and APIs for the Solaris environment, and any other SPARC-related information needed to generate HRTL code. The C back end is normally used as the back end. This results in a uqbtss (SPARC to SPARC) translator. In a similar way, a uqbtsp (SPARC to Pentium) translator, a uqbths (PA-RISC to SPARC) translator, and other translators can be instantiated.

In order to instantiate a new translator, the APIs and specification files for the source platform must be described. Testing of each step is important in order to ensure correctness of translation; hence, we provide ways to test the output from each step in the translation process.

The instantiation process consists of the following steps:

- 1. Binary file decoder support

- 2. Instruction decoding support

- 3. Instruction semantics support

- 4. Control transfer support

- 5. Procedural abstraction support

- 6. Machine-specific support

- 7. Code generation support

Each step is described in some detail in the following subsections assuming that the given API or specification is not already available. In those cases where it is available, there is no time overhead to reuse such an API or specification, other than to perform that step's tests.

## 3.1 Binary file Decoder Support

In order to support different binary file formats, such as ELF, PE or PRC, the UQBT framework exports a loader API called BinaryFile, which is an abstract class that makes available functions to:

- construct, load and unload binary files,

- extract information from sections,

- extract information from symbol tables (if any),

- extract information from relocation tables (if any),

- display/dump the contents of all headers, and

- obtain initial program state information, such as entry point(s), and determine whether a given address is a dynamically-linked address or not.

For a given binary file format BFF<sub>i</sub>, the BinaryFile API is realized by implementing the derived BFF<sub>i</sub>BinaryFile class. In this class, some extra functions are used to implement the BinaryFile interface, depending on the complexity of implementing the API functionality.

This first step is tested by displaying/dumping onto the standard output stream the contents of all headers and sections read from the file. These contents are then checked manually against the contents produced by a binary file dump tool, commonly distributed with operating systems these days. For example, in the Solaris environment, the elfdump tool displays the contents of an ELF's file headers. A typical size of information dumped is around 500 lines of ASCII text. Similar results are achieved by using GNU's objdump tool.

The UQBT framework provides a skeleton file bffDump.cc that is the basis for creating a binary file dumper. The program displays the raw contents of each of the headers and fields of the given binary file.

## 3.2 Instruction Decoding Support

This step is the most time consuming one in the instantiation process as the binary translator writer needs to become fully familiar with the  $M_s$  instruction set to be supported. This step involves reading through architecture manuals and representing the information for instructions in terms of the SLED language. SLED allows for describing the types of instructions in a given machine, the fields of such instructions, and the values of particular instruction fields. Describing the instructions, in essence, maps binary bit streams to assembly instructions. In our experience, depending on how complex the instruction set is, and how familiar the developer is with the instruction set and the SLED language, this step can take anywhere from 2 weeks to 2 months.

The New Jersey Machine Code toolkit (NJMCTK) not only supports the SLED language, but also supports an abstraction to decode and encode machine instructions. The decoding abstraction provides for a *matching* statement whose syntax resembles that of a C language switch statement, and whose semantics are equivalent to matching the series of bits that make up an instruction and returning the values of the variable fields of an instruction. In this way, a decoder (disassembler) of machine instructions can be written, and the time to do this is minimal (less than 1 day); in fact, it is possible to automatically generate such a decoder. This decoder is tested against an existing disassembler for the source machine through a series of test cases. This is possible as most UNIX(R) systems include a dis utility in their distribution or one is included as part of the GNU binutils.

Sample decoders are provided with the UQBT distribution. A skeleton driver program is provided to build a disassembler for any machine. The function disassembleOneInstruction is implemented as part of the matching file to be provided by the binary translator writer.

# 3.3 Instruction Semantics Support

Writing the SSL specification is routine once the SLED specification has been written, because by then the developer is very familiar with the instruction set. The learning curve for the SSL language is not too demanding. In our experience, writing an SSL specification takes about one third of the time that it takes to write the SLED specification.

We currently test an SSL specification using an extension to the decoder. Instead of dumping raw assembly information, we cause the decoder to dump RTL information. That information is manually checked against the assembly output.

We initially tested this step using an RTL encoder. That is, after generating RTL instructions, we would encode them using a different tool, and compare the execution results of the translated code against the execution of the source  $M_s$  binary program. We used the VPO optimizer for this

purpose since it operates on RTLs. However, VPO requires knowledge of live register information at each procedure call site, hence, only simple programs can be translated using this testing scheme, as no live register analysis has been done on the RTLs at this point in the translation process.

# 3.4 Control Transfer Support

The control transfer API is not formally specified, although it is hardcoded in the required code for a translator. Control transfer instructions such as branches and calls are matched against in the instruction decoder to transform control transfer M<sub>s</sub>-RTLs into an "in between" HRTL form that we call I-RTL I-RTL stands for "independent RTL", as they resemble HRTL instructions though their operands have not been obtained yet (these are obtained through procedural abstraction analysis).

This step is almost trivial and can be implemented in one day after looking at skeletons of existing translators.

## 3.5 Procedural Abstraction Support

The PAL specification is based on the operating system ABI conventions for setting up the call stack frame, parameter passing and calling conventions. Specifying this information takes little time (two days) once the information to be specified has been determined.

Testing of the PAL specification and the resultant HRTL instructions can only be done by compiling to the same machine, then comparing the execution results of the generated target binary against those of the source binary. For example, for a translation from a (SPARC,Solaris) binary, we compile HRTL back into a (SPARC,Solaris) binary and then compare the results of running the two programs.

Programs do not necessarily adhere to the OS ABI calling conventions. Therefore, commonly used non-ABI conventions need also be included in a PAL specification. Such cases are normally detected by running programs compiled by different compilers from the source platform; once a non-ABI convention is reached, the translator will warn the user about it.

# 3.6 Machine-specific Support

This step varies from machine to machine and involves the removal of machine-specific features that are not supported by the UQBT framework in a machine-independent way. The features are normally too specific to be available in multiple machines, and so the binary translator writer needs to provide some analysis support to transform I-RTL code that exhibits such features into HRTL code. Depending on the level of complexity of the feature at hand, this step can take anywhere from less than one week to one staff-month. Some of the support that we have introduced for different front ends was explained in §2.2.2.

## 3.7 Code Generation Support

This last step consists of choosing an existing back end and possibly adding specific support for the target machine. The C back end is the most versatile one and the one that takes the least amount of time in instantiating; all that is necessary is to use a C compiler on the target machine to compile the generated code.

#### The RTL Back End

In order to instantiate a  $M_t$ -RTL back end for a machine  $M_t$ , two steps are needed: create a HRTL to  $M_t$ -RTL translator, and support  $M_t$  in the optimizer (VPO in our case). We experimented with generating code for  $M_t$  machines that VPO already supported, so we only needed to write the  $M_t$ -RTL translator. This step requires writers to satisfy VPO's  $M_t$ -RTL invariant: that each  $M_t$ -RTL must map to one  $M_t$  assembly instruction. This is not technically difficult but does require care, for example, to properly "downshift" complex HRTL expressions to a sequence of simple  $M_t$ -RTLs.

Writing an  $M_t$ -RTL translator normally takes 3-5 staff-months for someone experienced with VPO. The difference in time required depends mainly on differences between the different target machines. For example, the ARM processor has limited support for immediate values in instructions. This means that constant addresses and values larger than 8 bits required additional work to implement. As another example, the ARM procedure call standard can cause a 64 bit floating point parameter to be split between memory and the stack, and extra translator code was required to deal with these.

## The Object Code Back End

Instantiation of an object code back end requires two steps: generating a HRTL to  $M_t$  translator (which provides the same challenges as generating a HRTL to  $M_t$ -RTL translator), and encoding the generated  $M_t$  machine code instructions into a binary stream that is then passed to a binary file encoder.

Translation of HRTL to  $M_t$  assembly code takes roughly one staff-month for integer-only support. If a SLED specification for the target machine can be reused, encoding into an  $M_t$  binary stream takes one day; otherwise, support for that encoding can take up to a month.

#### The JVML Back End

Using the JVML back end is as straightforward as using the C back end, except that the binary translator writer must be aware that the JVML back end generates code for data addresses by allocating a large array and placing read-only data at those addresses. Hence, if addresses in the source binary are too large, the target program will attempt to reserve a large amount of space when it starts, which might result in an out-of-memory condition. As previously mentioned, the

JVML back end was only tested when translating (SPARC,Solaris) binaries that made limited use of pointer operations; it did not support the full C memory model.

# 4 Experience

Researchers, students, and engineers have used the UQBT framework to experiment with translations between a number of different architectures. As researchers, our main focus was to experiment with new machine features in order to capture those features in a general framework, so that more machines could be supported by the specification languages and APIs we used. As engineers, we were interested in seeing how well the generated target binaries performed. We always tested their execution time against that of a natively-compiled binary running on the target platform to determine what overhead was introduced by the translation process. We were also interested in how well the translated binaries ran: that is, what experience a user would get from running them.

This section describes our experiences and those of our students in using the UQBT framework. We group those experiences based on the focus of interest when developing a particular translator: that is, whether most of the work was done in instantiating a new front end or in writing a new back end. Once such front ends and back ends are available, they can be mixed and matched to instantiate a particular translator of choice, by choosing the source  $M_s$  and target  $M_t$  platforms. We have made an effort to quantify the amount of time spent in writing such translators, noting that different levels of experience with UQBT imply differences in time needed to develop a particular component.

# 4.1 Experience with the Development of the Initial UQBT Framework